# 93AA76/86

## 8K/16K 1.8V Microwire<sup>®</sup> Serial EEPROM

## FEATURES

- Single supply operation down to 1.8V

- Low power CMOS technology

- 1 mA active current typical

- 5 µA standby current (typical) at 3.0V

- ORG pin selectable memory configuration

- 1024 x 8 or 512 x 16-bit organization (93AA76)

- 2048 x 8 or 1024 x 16-bit organization (93AA86)

- · Self-timed ERASE and WRITE cycles

- Automatic ERAL before WRAL

- · Power on/off data protection circuitry

- Industry standard 3-wire serial I/O

- Device status signal during ERASE/WRITE cycles

- Sequential READ function

- 1,000,000 ERASE/WRITE cycles guaranteed

- Data retention > 200 years

- 8-pin PDIP/SOIC package

- Temperature ranges available:

- Commercial (C): 0°C to +70°C

## DESCRIPTION

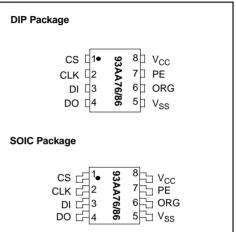

The Microchip Technology Inc. 93AA76/86 are 8K and 16K low voltage serial Electrically Erasable PROMs. The device memory is configured as x8 or x16 bits depending on the ORG pin setup. Advanced CMOS technology makes these devices ideal for low power non-volatile memory applications. These devices also have a Program Enable (PE) pin to allow the user to write protect the entire contents of the memory array. The 93AA76/86 is available in standard 8-pin DIP and 8-pin surface mount SOIC packages.

#### PACKAGE TYPES

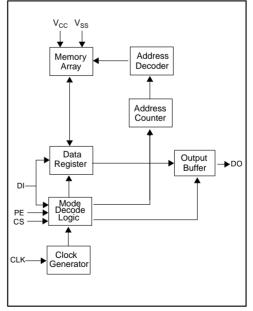

## **BLOCK DIAGRAM**

Microwire is a registered trademark of National Semiconductor Incorporated.

## **1.0 ELECTRICAL CHARACTERISTICS**

#### 1.1 <u>Maximum Ratings\*</u>

| VCC                                              | .0V |

|--------------------------------------------------|-----|

| All inputs and outputs w.r.t. VSS0.6V to Vcc +1. | .0V |

| Storage temperature65°C to +150                  | С°С |

| Ambient temp. with power applied65°C to +125     | 5°C |

| Soldering temperature of leads (10 seconds)+300  | °С  |

| ESD protection on all pins4                      | kV  |

\*Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability

## TABLE 1-1: PIN FUNCTION TABLE

| Name | Function             |

|------|----------------------|

| CS   | Chip Select          |

| CLK  | Serial Data Clock    |

| DI   | Serial Data Input    |

| DO   | Serial Data Output   |

| Vss  | Ground               |

| ORG  | Memory Configuration |

| PE   | Program Enable       |

| Vcc  | Power Supply         |

#### 1.2 AC Test Conditions

AC Waveform:

| VLO = 2.0V       |          |

|------------------|----------|

| VHI = Vcc - 0.2V | (Note 1) |

| VHI = 4.0V for   | (Note 2) |

Timing Measurement Reference Level

| Input   | 0.5 Vcc             |         |

|---------|---------------------|---------|

| Outp    | ut                  | 0.5 Vcc |

| Note 1: | For Vcc $\leq 4.0V$ |         |

| 2:      | For VCC > 4.0V      |         |

## TABLE 1-2: DC CHARACTERISTICS

| Applicable over recommended operating ranges shown below unless otherwise noted:<br>Vcc = +1.8V to +6.0V<br>Commercial (C): Tamb = 0°C to +70°C |           |         |           |          |                                                                                            |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----------|----------|--------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                                                                                                       | Symbol    | Min.    | Max.      | Units    | Conditions                                                                                 |  |  |  |

| High level input voltage                                                                                                                        | VIH1      | 2.0     | Vcc +1    | V        | Vcc ≥ 2.7V                                                                                 |  |  |  |

|                                                                                                                                                 | VIH2      | 0.7 Vcc | Vcc +1    | V        | Vcc < 2.7V                                                                                 |  |  |  |

| Low level input voltage                                                                                                                         | VIL1      | -0.3    | 0.8       | V        | Vcc ≥ 2.7V                                                                                 |  |  |  |

|                                                                                                                                                 | VIL2      | -0.3    | 0.2 Vcc   | V        | Vcc < 2.7V                                                                                 |  |  |  |

| Low level output voltage                                                                                                                        | VOL1      | _       | 0.4       | V        | IOL = 2.1 mA; VCC = 4.5V                                                                   |  |  |  |

|                                                                                                                                                 | VOL2      | _       | 0.2       | V        | IoL =100 μA; Vcc = Vcc Min.                                                                |  |  |  |

| High level output voltage                                                                                                                       | VOH1      | 2.4     | _         | V        | Іон = -400 μA; Vcc = 4.5V                                                                  |  |  |  |

|                                                                                                                                                 | VOH2      | Vcc-0.2 | _         | V        | Іон = -100 μA; Vcc = Vcc Min.                                                              |  |  |  |

| Input leakage current                                                                                                                           | lu lu     | -10     | 10        | μΑ       | VIN = 0.1V to VCC                                                                          |  |  |  |

| Output leakage current                                                                                                                          | ILO       | -10     | 10        | μΑ       | VOUT = 0.1V to VCC                                                                         |  |  |  |

| Pin capacitance<br>(all inputs/outputs)                                                                                                         | CINT      | —       | 7         | pF       | (Note Note:)<br>Tamb = +25°С, FcLк = 1 MHz                                                 |  |  |  |

| Operating current                                                                                                                               | Icc write | _       | 3         | mA       | Vcc = 5.5V                                                                                 |  |  |  |

|                                                                                                                                                 | Icc read  | —       | 1<br>500  | mA<br>μA | FCLK = 3 MHz; VCC = 5.5V<br>FCLK = 1 MHz; VCC = 3.0V                                       |  |  |  |

| Standby current                                                                                                                                 | Iccs      |         | 100<br>30 | μΑ<br>μΑ | CLK = CS = 0V; Vcc = 5.5V $CLK = CS = 0V; Vcc = 3.0V$ $DI = PE = Vss$ $ORG = Vss  or  Vcc$ |  |  |  |

Note: This parameter is periodically sampled and not 100% tested.

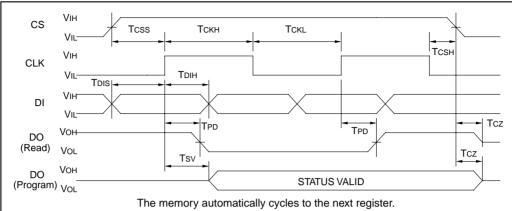

### TABLE 1-3: AC CHARACTERISTICS

Applicable over recommended operating ranges shown below unless otherwise noted: Vcc = +1.8V to +6.0V

Commercial (C): Tamb =  $0^{\circ}$ C to +70°C

|                          |            | -                 |                   |                   |                                                                                                                                                                                   |

|--------------------------|------------|-------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                | Symbo<br>I | Min.              | Max.              | Units             | Conditions                                                                                                                                                                        |

| Clock frequency          | FCLK       | _                 | 3<br>2<br>1       | MHz<br>MHz<br>Mhz | $4.5V \le Vcc \le 6.0V$<br>$2.5V \le Vcc \le 4.5V$<br>$1.8V \le Vcc < 2.5V$                                                                                                       |

| Clock high time          | Тскн       | 200<br>300<br>500 | _                 | ns<br>ns<br>ns    | 4.5V ≥Vcc ≤ 6.0V<br>2.5V ≤Vcc < 4.5V<br>1.8V ≤Vcc < 2.5V                                                                                                                          |

| Clock low time           | TCKL       | 100<br>200<br>500 | -                 | ns<br>ns<br>ns    | 4.5V ≤ Vcc ≤ 6.0V<br>2.5V ≤ Vcc < 4.5V<br>1.8V ≤ Vcc < 2.5V                                                                                                                       |

| Chip select setup time   | Tcss       | 50<br>100<br>250  | _                 | ns<br>ns<br>ns    | $\begin{array}{l} 4.5V \leq Vcc \leq 6.0V, \mbox{ Relative to CLK} \\ 2.5V \leq Vcc < 4.5V, \mbox{ Relative to CLK} \\ 1.8V \leq Vcc < 2.5V, \mbox{ Relative to CLK} \end{array}$ |

| Chip select hold time    | Тсѕн       | 0                 | —                 | ns                | $1.8V \leq Vcc \leq 6.0V$                                                                                                                                                         |

| Chip select low time     | TCSL       | 250               | —                 | ns                | $1.8V \le VCC \le 6.0V$ , Relative to CLK                                                                                                                                         |

| Data input setup time    | TDIS       | 50<br>100<br>250  | _                 | ns<br>ns<br>ns    | $\begin{array}{l} 4.5V \leq Vcc \leq 6.0V, \mbox{ Relative to CLK} \\ 2.5V \leq Vcc < \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                         |

| Data input hold time     | Тын        | 50<br>100<br>250  | -                 | ns<br>ns<br>ns    | $\begin{array}{l} 4.5V \leq Vcc \leq 6.0V, \mbox{ Relative to CLK} \\ 2.5V \leq Vcc < 4.5V, \mbox{ Relative to CLK} \\ 1.8V \leq Vcc < 2.5V, \mbox{ Relative to CLK} \end{array}$ |

| Data output delay time   | TPD        | _                 | 100<br>250<br>500 | ns<br>ns<br>ns    | $\begin{array}{l} 4.5V \ \leq Vcc \ \leq 6.0V, \ CL = 100 \ pF \\ 2.5V \ \leq Vcc \ < 4.5V, \ CL = 100 \ pF \\ 1.8V \ \leq Vcc \ < 2.5V, \ CL = 100 \ pF \end{array}$             |

| Data output disable time | Tcz        | _                 | 100<br>500        | ns<br>ns          | 4.5V ≤ Vcc ≤ 5.5V (Note 1)<br>1.8V ≤ Vcc < 4.5V (Note 1)                                                                                                                          |

| Status valid time        | Tsv        |                   | 200<br>300<br>500 | ns<br>ns<br>ns    | $\begin{array}{l} 4.5V \ \geq Vcc \ \leq 6.0V, \ CL = 100 \ pF \\ 2.5V \ \leq Vcc \ < 4.5V, \ CL = 100 \ pF \\ 1.8V \ \leq Vcc \ < 2.5V, \ CL = 100 \ pF \end{array}$             |

| Program cycle time       | Тwc        | —                 | 5                 | ms                | ERASE/WRITE mode                                                                                                                                                                  |

|                          | TEC        | _                 | 15                | ms                | ERAL mode                                                                                                                                                                         |

|                          | TwL        | _                 | 30                | ms                | WRAL mode                                                                                                                                                                         |

| Endurance                | -          | 1M                | _                 | cycles            | 25°C, Vcc = 5.0V, Block Mode (Note 2)                                                                                                                                             |

Note 1: This parameter is periodically sampled and not 100% tested.

2: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on our website.

| Instruction | SB | Opcode | Address                      | Data In  | Data Out  | Req. CLK Cycles |

|-------------|----|--------|------------------------------|----------|-----------|-----------------|

| READ        | 1  | 10     | X A8 A7 A6 A5 A4 A3 A2 A1 A0 | _        | D15 - D0  | 29              |

| EWEN        | 1  | 00     | 1 1 X X X X X X X X          | —        | High-Z    | 13              |

| ERASE       | 1  | 11     | X A8 A7 A6 A5 A4 A3 A2 A1 A0 | _        | (RDY/BSY) | 13              |

| ERAL        | 1  | 00     | 1 0 X X X X X X X X          | —        | (RDY/BSY) | 13              |

| WRITE       | 1  | 01     | X A8 A7 A6 A5 A4 A3 A2 A1 A0 | D15 - D0 | (RDY/BSY) | 29              |

| WRAL        | 1  | 00     | 0 1 X X X X X X X X          | D15 - D0 | (RDY/BSY) | 29              |

| EWDS        | 1  | 00     | 0 0 X X X X X X X X          | —        | High-Z    | 13              |

#### TABLE 1-4: INSTRUCTION SET FOR 93AA76: ORG=1 (X16 ORGANIZATION)

#### TABLE 1-5: INSTRUCTION SET FOR 93AA76: ORG=0 (X8 ORGANIZATION)

| Instruction | SB | Opcode | Address                         | Data In | Data Out  | Req. CLK<br>Cycles |

|-------------|----|--------|---------------------------------|---------|-----------|--------------------|

| READ        | 1  | 10     | X A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | _       | D7 - D0   | 22                 |

| EWEN        | 1  | 00     | 1 1 X X X X X X X X             | _       | High-Z    | 14                 |

| ERASE       | 1  | 11     | X A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | _       | (RDY/BSY) | 14                 |

| ERAL        | 1  | 00     | 1 0 X X X X X X X X             | _       | (RDY/BSY) | 14                 |

| WRITE       | 1  | 01     | X A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | D7 - D0 | (RDY/BSY) | 22                 |

| WRAL        | 1  | 00     | 0 1 X X X X X X X X             | D7 - D0 | (RDY/BSY) | 22                 |

| EWDS        | 1  | 00     | 0 0 X X X X X X X X             | _       | High-Z    | 14                 |

#### TABLE 1-6: INSTRUCTION SET FOR 93AA86: ORG=1 (X16 ORGANIZATION)

| Instruction | SB | Opcode | Address                       | Data In  | Data Out  | Req. CLK Cycles |

|-------------|----|--------|-------------------------------|----------|-----------|-----------------|

| READ        | 1  | 10     | A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | —        | D15 - D0  | 29              |

| EWEN        | 1  | 00     | 1 1 X X X X X X X X           | —        | High-Z    | 13              |

| ERASE       | 1  | 11     | A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | —        | (RDY/BSY) | 13              |

| ERAL        | 1  | 00     | 1 0 X X X X X X X X           | —        | (RDY/BSY) | 13              |

| WRITE       | 1  | 01     | A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | D15 - D0 | (RDY/BSY) | 29              |

| WRAL        | 1  | 00     | 0 1 X X X X X X X X           | D15 - D0 | (RDY/BSY) | 29              |

| EWDS        | 1  | 00     | 0 0 X X X X X X X X           | —        | High-Z    | 13              |

## TABLE 1-7: INSTRUCTION SET FOR 93AA86: ORG=0 (X8 ORGANIZATION)

| Instruction | SB | Opcode | Address                           | Data In | Data Out  | Req. CLK Cycles |

|-------------|----|--------|-----------------------------------|---------|-----------|-----------------|

| READ        | 1  | 10     | A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | _       | D7 - D0   | 22              |

| EWEN        | 1  | 00     | 1 1 X X X X X X X X               | —       | High-Z    | 14              |

| ERASE       | 1  | 11     | A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | -       | (RDY/BSY) | 14              |

| ERAL        | 1  | 00     | 1 0 X X X X X X X X               | _       | (RDY/BSY) | 14              |

| WRITE       | 1  | 01     | A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 | D7 - D0 | (RDY/BSY) | 22              |

| WRAL        | 1  | 00     | 0 1 X X X X X X X X               | D7 - D0 | (RDY/BSY) | 22              |

| EWDS        | 1  | 00     | 0 0 X X X X X X X X               | _       | High-Z    | 14              |

## 2.0 PRINCIPLES OF OPERATION

When the ORG pin is connected to Vcc, the x16 organization is selected. When it is connected to ground, the x8 organization is selected. Instructions, addresses and write data are clocked into the DI pin on the rising edge of the clock (CLK). The DO pin is normally held in a high-Z state except when reading data from the device, or when checking the READY/BUSY status during a programming operation. The READY/BUSY status can be verified during an Erase/Write operation by polling the DO pin; DO low indicates that programming is still in progress, while DO high indicates the device is ready. The DO will enter the high impedance state on the falling edge of the CS.

#### 2.1 START Condition

The START bit is detected by the device if CS and DI are both HIGH with respect to the positive edge of CLK for the first time.

Before a START condition is detected, CS, CLK, and DI may change in any combination (except to that of a START condition), without resulting in any device operation (READ, WRITE, ERASE, EWEN, EWDS, ERAL, and WRAL). As soon as CS is HIGH, the device is no longer in the standby mode.

An instruction following a START condition will only be executed if the required amount of opcode, address and data bits for any particular instruction are clocked in.

After execution of an instruction (i.e., clock in or out of the last required address or data bit) CLK and DI become don't care bits until a new start condition is detected.

## 2.2 <u>DI/DO</u>

It is possible to connect the Data In and Data Out pins together. However, with this configuration it is possible for a "bus conflict" to occur during the "dummy zero" that precedes the READ operation, if A0 is a logic HIGH level. Under such a condition the voltage level seen at Data Out is undefined and will depend upon the relative impedances of Data Out and the signal source driving A0. The higher the current sourcing capability of A0, the higher the voltage at the Data Out pin.

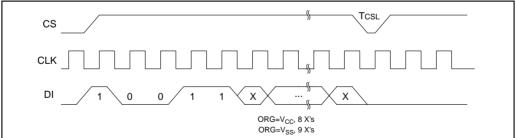

#### 2.3 <u>Erase/Write Enable and Disable</u> (EWEN, EWDS)

The 93AA76/86 powers up in the Erase/Write Disable (EWDS) state. All programming modes must be preceded by an Erase/Write Enable (EWEN) instruction. Once the EWEN instruction is executed, programming remains enabled until an EWDS instruction is executed or Vcc is removed from the device. To protect against accidental data disturb, the EWDS instruction can be used to disable all Erase/Write functions and should follow all programming operations. Execution of a READ instruction is independent of both the EWEN and EWDS instructions.

#### 2.4 Data Protection

During power-up, all programming modes of operation are inhibited until Vcc has reached a level greater than 1.4V. During power-down, the source data protection circuitry acts to inhibit all programming modes when Vcc has fallen below 1.4V.

The EWEN and EWDS commands give additional protection against accidentally programming during normal operation.

After power-up, the device is automatically in the EWDS mode. Therefore, an EWEN instruction must be performed before any ERASE or WRITE instruction can be executed.

## 3.0 DEVICE OPERATION

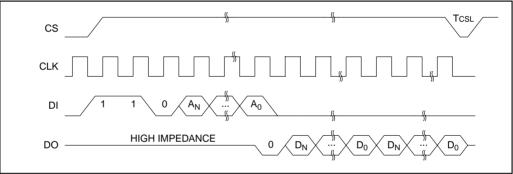

### 3.1 <u>READ</u>

The READ instruction outputs the serial data of the addressed memory location on the DO pin. A dummy zero bit precedes the 16 bit (x16 organization) or 8 bit (x8 organization) output string. The output data bits will toggle on the rising edge of the CLK and are stable after the specified time delay (TPD). Sequential read is possible when CS is held high and clock transitions continue. The memory address pointer will automatically increment and output data sequentially.

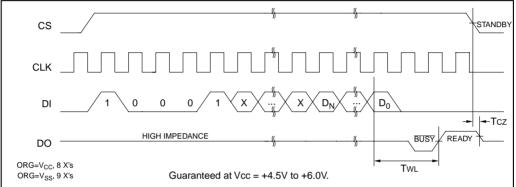

#### 3.2 <u>ERASE</u>

The ERASE instruction forces all data bits of the specified address to the logical "1" state. The self-timed programming cycle is initiated on the rising edge of CLK as the last address bit (A0) is clocked in. At this point, the CLK, CS, and DI inputs become don't cares.

The DO pin indicates the READY/BUSY status of the device if the CS is high. The READY/BUSY status will be displayed on the DO pin until the next start bit is received as long as CS is high. Bringing the CS low will place the device in standby mode and cause the DO pin to enter the high impedance state. DO at logical "0" indicates that programming is still in progress. DO at logical "1" indicates that the register at the specified address has been erased and the device is ready for another instruction.

The ERASE cycle takes 3 ms per word (Typical).

#### 3.3 <u>WRITE</u>

The WRITE instruction is followed by 16 bits (or by 8 bits) of data to be written into the specified address. The self-timed programming cycle is initiated on the rising edge of CLK as the last data bit (D0) is clocked in. At this point, the CLK, CS, and DI inputs become don't cares.

The DO pin indicates the READY/BUSY status of the device if the CS is high. The READY/BUSY status will be displayed on the DO pin until the next start bit is received as long as CS is high. Bringing the CS low will place the device in standby mode and cause the DO pin to enter the high impedance state. DO at logical "0" indicates that programming is still in progress. DO at logical "1" indicates that the register at the specified address has been written and the device is ready for another instruction.

The WRITE cycle takes 3 ms per word (Typical).

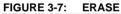

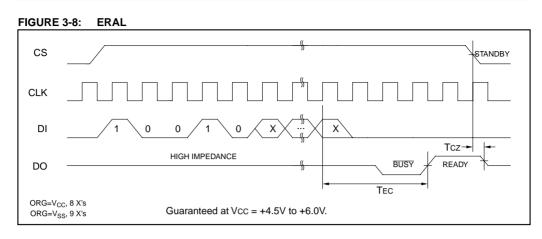

#### 3.4 Erase All (ERAL)

The ERAL instruction will erase the entire memory array to the logical "1" state. The ERAL cycle is identical to the ERASE cycle except for the different opcode. The ERAL cycle is completely self-timed and commences on the rising edge of the last address bit (A0). Note that the least significant 8 or 9 address bits are don't care bits, depending on selection of x16 or x8 mode. Clocking of the CLK pin is not necessary after the device has entered the self clocking mode. The ERAL instruction is guaranteed at Vcc = +4.5V to +6.0V.

The DO pin indicates the READY/BUSY status of the device if the CS is high. The READY/BUSY status will be displayed on the DO pin until the next start bit is received as long as CS is high. Bringing the CS low will place the device in standby mode and cause the DO pin to enter the high impedance state. DO at logical "0" indicates that programming is still in progress. DO at logical "1" indicates that the entire device has been erased and is ready for another instruction.

The ERAL cycle takes 15 ms maximum (8 ms typical).

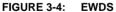

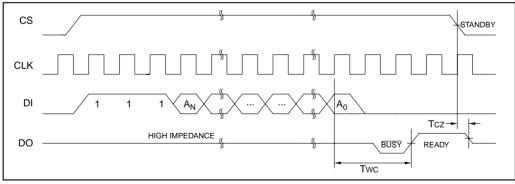

#### 3.5 Write All (WRAL)

The WRAL instruction will write the entire memory array with the data specified in the command. The WRAL cycle is completely self-timed and commences on the rising edge of the last address bit (A0). Note that the least significant 8 or 9 address bits are don't cares, depending on selection of x16 or x8 mode. Clocking of the CLK pin is not necessary after the device has entered the self clocking mode. The WRAL command does include an automatic ERAL cycle for the device. Therefore, the WRAL instruction does not require an ERAL instruction but the chip must be in the EWEN status. The WRAL instruction is guaranteed at Vcc = +4.5V to +6.0V.

The DO pin indicates the READY/BUSY status of the device if the CS is high. The READY/BUSY status will be displayed on the DO pin until the next start bit is received as long as CS is high. Bringing the CS low will place the device in standby mode and cause the DO pin to enter the high impedance state. DO at logical "0" indicates that programming is still in progress. DO at logical "1" indicates that the entire device has been written and is ready for another instruction.

The WRAL cycle takes 30 ms maximum (16 ms typical).

FIGURE 3-2: READ

## 93AA76/86

## FIGURE 3-5: WRITE

## 4.0 PIN DESCRIPTIONS

#### 4.1 Chip Select (CS)

A HIGH level selects the device. A LOW level deselects the device and forces it into standby mode. However, a programming cycle which is already initiated will be completed, regardless of the CS input signal. If CS is brought LOW during a program cycle, the device will go into standby mode as soon as the programming cycle is completed.

CS must be LOW for 250 ns minimum (TCSL) between consecutive instructions. If CS is LOW, the internal control logic is held in a RESET status.

#### 4.2 Serial Clock (CLK)

The Serial Clock is used to synchronize the communication between a master device and the 93AA76/86. Opcode, address, and data bits are clocked in on the positive edge of CLK. Data bits are also clocked out on the positive edge of CLK.

CLK can be stopped anywhere in the transmission sequence (at HIGH or LOW level) and can be continued anytime with respect to clock HIGH time (TCKH) and clock LOW time (TCKL). This gives the controlling master freedom in preparing opcode, address, and data.

CLK is a "Don't Care" if CS is LOW (device deselected). If CS is HIGH, but START condition has not been detected, any number of clock cycles can be received by the device without changing its status (i.e., waiting for START condition).

CLK cycles are not required during the self-timed WRITE (i.e., auto ERASE/WRITE) cycle.

After detection of a start condition the specified number of clock cycles (respectively LOW to HIGH transitions of CLK) must be provided. These clock cycles are required to clock in all opcode, address, and data bits before an instruction is executed (see Table 1-4 through Table 1-7 for more details). CLK and DI then become don't care inputs waiting for a new start condition to be detected.

Note: CS must go LOW between consecutive instructions, except when performing a sequential read (Refer to Section 3.1 for more detail on sequential reads).

## 4.3 Data In (DI)

Data In is used to clock in a START bit, opcode, address, and data synchronously with the CLK input.

## 4.4 Data Out (DO)

Data Out is used in the READ mode to output data synchronously with the CLK input (TPD after the positive edge of CLK).

This pin also provides READY/BUSY status information during ERASE and WRITE cycles. READY/BUSY status information is available when CS is high. It will be displayed until the next start bit occurs as long as CS stays high.

## 4.5 Organization (ORG)

When ORG is connected to Vcc, the x16 memory organization is selected. When ORG is tied to Vss, the x8 memory organization is selected. There is an internal pull-up resistor on the ORG pin that will select x16 organization when left unconnected.

## 4.6 Program Enable (PE)

This pin allows the user to enable or disable the ability to write data to the memory array. If the PE pin is floated or tied to Vcc, the device can be programmed. If the PE pin is tied to Vss, programming will be inhibited. There is an internal pull-up on this device that enables programming if this pin is left floating.

© 1998 Microchip Technology Inc.

## 93AA76/86

NOTES:

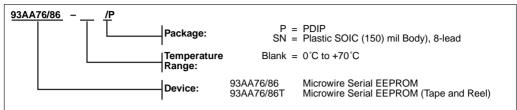

#### 93AA76/86 Product Identification System

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following: 1. Your local Microchip sales office

- The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

- 3. The Microchip Worldwide Web Site (www.microchip.com)

## WORLDWIDE SALES AND SERVICE

## AMERICAS

#### Corporate Office

Microchip Technology Inc. 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 602-786-7200 Fax: 602-786-7277 Technical Support: 602 786-7627 Web: http://www.microchip.com

#### Atlanta

Microchip Technology Inc. 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

Microchip Technology Inc. 5 Mount Royal Avenue Marlborough, MA 01752 Tel: 508-480-9990 Fax: 508-480-8575

#### Chicago

Microchip Technology Inc. 333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

#### Dallas

Microchip Technology Inc. 14651 Dallas Parkway, Suite 816 Dallas, TX 75240-8809 Tel: 972-991-7177 Fax: 972-991-8588

#### Dayton

Microchip Technology Inc. Two Prestige Place, Suite 150 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

#### Detroit

Microchip Technology Inc. 42705 Grand River, Suite 201 Novi, MI 48375-1727 Tel: 248-374-1888 Fax: 248-374-2878

#### Los Angeles

Microchip Technology Inc. 18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 714-263-1888 Fax: 714-263-1338

#### New York

Microchip Technology Inc. 150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 516-273-5305 Fax: 516-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### **AMERICAS** (continued)

#### Toronto

Microchip Technology Inc. 5925 Airport Road, Suite 200 Mississauga, Ontario L4V 1W1, Canada Tel: 905-405-6279 Fax: 905-405-6253

## ASIA/PACIFIC

#### Hona Kona

Microchip Asia Pacific RM 3801B, Tower Two Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2-401-1200 Fax: 852-2-401-3431

#### India

Microchip Technology Inc. India Liaison Office No. 6, Legacy, Convent Road Bangalore 560 025, India Tel: 91-80-229-0061 Fax: 91-80-229-0062

#### Japan

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa 222-0033 Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

#### Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934

#### Shanghai

ı

Ø

-

Microchip Technology RM 406 Shanghai Golden Bridge Bldg. 2077 Yan'an Road West, Hong Qiao District Shanghai, PRC 200335 Tel: 86-21-6275-5700 Fax: 86 21-6275-5060

## **ASIA/PACIFIC** (continued)

#### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore 188980 Tel: 65-334-8870 Fax: 65-334-8850

#### Taiwan, R.O.C

Microchip Technology Taiwan 10F-1C 207 Tung Hua North Road Taipei, Taiwan, ROC Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### EUROPE

#### United Kingdom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44-1189-21-5858 Fax: 44-1189-21-5835 Franco

Arizona Microchip Technology SARL Zone Industrielle de la Bonde 2 Rue du Buisson aux Fraises 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann-Ring 125 D-81739 Müchen, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

#### Italv

Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-39-6899939 Fax: 39-39-6899883

6/11/98

**DNV Certification. Inc** DNV MSC USA The Net Accredited by the ByA ED 8 2 ANSI-RAB ¢ **ISO 9001** REGISTERED FIRM

Microchip received ISO 9001 Quality System certification for its worldwide headquarters, design, and wafer fabrication facilities in January, 1997. Our field-programmable PICmicro™ 8-bit MCUs, Serial EEPROMs, related specialty memory products and development systems conform to the stringent quality standards of the International Standard Organization (ISO).

All rights reserved. © 1998, Microchip Technology Incorporated, USA. 7/98 💭 Printed on recycled paper.

Information ontained in this philorition regarding doing applications and the like is intended for suggestion only and my he suggested by updates. Bo representation or warranty is given and no liability is examely Microthip Pathology Incorporated with respect to the annary or use of and information, or infringement of patents or other intellational property rights arising from and use or otherwise. Use of Microthip's products as critical components in life suggest systems is not anthrized excit with express within approad by Microthip. No licenses are convect, simplicity or otherwise, under any intellational property rights. The Microthip logs and rate are registered tackmarks of Microthip Technology Inc. in the U.S.A. and other controles. All rights reserved, All other trachmarks metricand herein are the property of their respective comprise.